-

chyba ma być reset _ config zamiast reset config

Mikrokontrolery ARM

27 Lut 2013 22:11

Odpowiedzi: 16 Wyświetleń: 2763

-

-

Jeśli masz JTAGa z dwoma osobnymi resetami (TRST i SRST) to do wywołania OpenOCD dodaj: -c "reset_config trst_and_srst" lub -c "reset_config trst_and_srst srst_pulls_trst" 4\/3!!

Mikrokontrolery ARM

10 Lip 2012 22:11

Odpowiedzi: 2 Wyświetleń: 1677

-

Nie znalazłeś odpowiedzi? Zadaj pytanie Sztucznej Inteligencji

-

Spróbuj dodać komendę: -c "reset_config none" w 'OpenOCD Options:' w oknie konfiguracji debugowania.

Mikrokontrolery ARM

25 Mar 2017 20:54

Odpowiedzi: 4 Wyświetleń: 2481

-

-

Chiński stlink, więc polecam sprawdzić: reset_config none separate

Mikrokontrolery ARM

23 Lis 2017 18:46

Odpowiedzi: 7 Wyświetleń: 1179

-

Spróbuj uruchomić OpenOCD z takimi komendami na początek: openocd -f <to-co-miałeś> -c "reset_config srst_only; init; reset halt; shutdown;" Spróbuj też: openocd -f <to-co-miałeś> -c "reset_config srst_only connect_assert_srst; init; reset halt; shutdown;" oraz: openocd -f <to-co-miałeś> -c "reset_config none; init; reset halt; shutdown;"...

Mikrokontrolery ARM

04 Lip 2016 18:33

Odpowiedzi: 20 Wyświetleń: 1992

-

-

1. Próbowałeś podłączyć się do układu który jest pod resetem? W OpenOCD da się to zrobić do wywołania dokładając np. -c "reset_config srst_nogate connect_assert_srst" 2. Co do problemu który obserwujesz, to może nowsza/rozwojowa wersja OpenOCD by tu zadziałała?

Mikrokontrolery ARM

14 Lip 2019 21:19

Odpowiedzi: 7 Wyświetleń: 804

-

Koledzy, czy Wy naprawdę nie widzicie bezsensu tej sytuacji? Dokładnie! Zamiast się tak męczyć, autor tematu mógł sobie po prostu kupić gotowe urządzenie w najbliższej klimatyzowanej galerii handlowej, zamiast się tak męczyć próbując zrobić coś samemu... Bez obrazy, ale Twoje nachalne wciskanie w co drugim temacie Keila jest już męczące. Jak widać...

Mikrokontrolery ARM

14 Kwi 2020 18:50

Odpowiedzi: 174 Wyświetleń: 12930

-

I Zylin I GDB Hardware Debug korzystają z OpenOCD jako serwera GDB. OpenOCD odpalam jako: openocd.exe -f interface/jtag-lock-pick_tiny_2.cfg -f target/stm32f1x.cfg -c "adapter_khz 1000; reset_config trst_and_srst separate; $_TARGETNAME configure -rtos auto" W gdb hardware debugging: DSF Launcher, komendy inicjujące: monitor reset halt, monitor poll,...

Mikrokontrolery ARM

14 Paź 2024 17:50

Odpowiedzi: 27 Wyświetleń: 5847

-

Bez mikrokontrolera gadałby to co widzisz właśnie [; Możesz zawsze spróbować zmniejszyć prędkość JTAGa (komenda jtag_khz) openocd -f interface\parport.cfg -f target\at91sam7sx.cfg -c "jtag_khz XXX" Możesz też poexperymentować z reset_config, np. openocd -f interface\parport.cfg -f target\at91sam7sx.cfg -c "jtag_khz XXX" -c "reset_config trst_and_srst"...

Mikrokontrolery ARM

21 Lis 2012 11:35

Odpowiedzi: 14 Wyświetleń: 2542

-

Info : clock speed 1000 kHz Error: SWD-DP OVERRUN - check clock, memaccess, or reduce swd speed Error: SWD-DP OVERRUN - check clock, memaccess, or reduce swd speed Przesadziłeś z zegarem - zmniejsz go na max 800 (z mojego doświadczenia). Config dla LPC1768 (używam do LPC1758) Musisz zmodyfikować, bo masz mniej flash. # Versaloon # interface vsllink...

Mikrokontrolery ARM

26 Maj 2014 17:52

Odpowiedzi: 9 Wyświetleń: 2814

-

W tym ST-linku pin reset nie działa albo jest to reset od SWIM'a. Żeby to jakoś ruszyło to trzeba poprawić config aby nie używał srst : source [find interface/stlink-v2.cfg] transport select hla_swd source [find target/stm32f1x.cfg] reset_config none separate

Mikrokontrolery ARM

31 Lip 2018 15:51

Odpowiedzi: 14 Wyświetleń: 1533

-

Mi działa z: #daemon configuration telnet_port 4444 gdb_port 3333 #interface interface ft2232 ft2232_device_desc "Olimex OpenOCD JTAG A" ft2232_layout "olimex-jtag" ft2232_vid_pid 0x15BA 0x0003 jtag_speed 50 #use combined on interfaces or targets that can't set TRST/SRST separately reset_config trst_and_srst separate #jtag scan chain #format L IRC IRCM...

Mikrokontrolery ARM

16 Kwi 2009 14:54

Odpowiedzi: 30 Wyświetleń: 8775

-

-

Masz zapewne źle podłączonego JTAGa (brak połączenia linii SRST). Zamiast mieszać w plikach konfiguracyjnych wystarczy nową komendę dodać do wywołania OpenOCD: $ openocd -f ... -f ... -c "reset_config none"

Mikrokontrolery ARM

27 Sty 2016 12:03

Odpowiedzi: 5 Wyświetleń: 1344

-

Info : stm32f4x.cpu: hardware has 0 breakpoints, 0 watchpoints Powinno być 6 i 4 (albo coś takiego). Jak jest 0 i 0 (albo jakieś inne bezsensowne wartości), to nawet nie ma co próbować dalszych kroków. Proponuję uruchamiać OpenOCD (tylko pierwszy raz po wyłączeniu zasilania) z wciśniętym przyciskiem reset na płytce. Proponuję też dodać do wywołania...

Mikrokontrolery ARM

02 Kwi 2013 04:27

Odpowiedzi: 4 Wyświetleń: 2088

-

Zmniejsz no trochę ten obrazek... Wystarczy link do niego, nie każdy musi go widzieć za każdym razem w pełnym rozmiarze. Config do target'u to ten, który był dostarczony razem z OpenOCD (AT91SAM7X256), tam opcje reset_config srst_only srst_pulls_trst były już wpisane. Czy mimo to mogę użyć innych? Możesz to po prostu zmienić... Jeśli Twoja płytka ma...

Mikrokontrolery ARM

21 Sty 2012 17:58

Odpowiedzi: 18 Wyświetleń: 2549

-

Niekoniecznie powinien się tam od razu zatrzymywać - jeśli ST zrobiło magiczny bootloader który zawsze startuje po resecie, to nic na to nie poradzisz. Ciężko mi coś powiedzieć, bo nie mam tej płytki i nigdy nie próbowałem jej używać. Przypuszczam jednak, że powinna działać, bo w OpenOCD jest config właśnie pod nią (w boards). 4\/3!!

Mikrokontrolery ARM

26 Gru 2013 16:57

Odpowiedzi: 13 Wyświetleń: 3069

-

Dobra już znalazłem jak podawać komendy ale dalej nie moge się poprawnie połączyć. Jaki typ resetu mam ustawić z srst_only nie działa . Dodano po 11 -f interface/stlink-v2.cfg -c"reset_config srst_only" -c "adapter_nsrst_assert_width 100" -c "adapter_nsrst_delay 100" -f target/stm32f0x_stlink.cfg Open On-Chip Debugger 0.7.0 (2013-05-05-10:44) Licensed...

Mikrokontrolery ARM

28 Lis 2013 22:22

Odpowiedzi: 14 Wyświetleń: 2127

-

Przede wszystkim o pomoc powinieneś się zwrócić do osoby która sprzedała Ci JTAGa i dołączyła do OpenOCD (nielegalnie dystrybuowanego zresztą) jakieś dziwaczne pliki. Dalej idąc - odpalasz OpenOCD używając DWÓCH plików konfiguracyjnych, linia reset_config jest też w tym drugim (target/stm32.cfg) - oryginalnym. Tam też musisz to zmienić, albo zakomentować...

Mikrokontrolery ARM

02 Maj 2010 13:06

Odpowiedzi: 9 Wyświetleń: 2221

-

Dzięki za uwagę. Zauważyłem, że podczas debugowania niektóre rzeczy zostają (w innych odrębnych przypadkach). Jeśli używasz standardowych konfigów do OpenOCD, to dodaj do jego wywołania coś takiego: -c "reset_config trst_and_srst" Domyślnie OpenOCD zakłada, że JTAG nie ma pinów resetu i w przypadku Cortex-M3 resetuje go specjalnym rejestrem rdzenia....

Mikrokontrolery ARM

07 Lip 2011 06:41

Odpowiedzi: 23 Wyświetleń: 3407

-

Taa... znów coś poknociłem. Mam programować Atmege32, a config OpenOCD wziąłem dla AVR32 :). Z tym, że jak się zorientowałem, to użyłem konfiga dla AtMega128 i wtedy też dostałem błędy. Sprawa kończyła się segfaultem OpenOCD. Ale w tej chwili jestem poza domem i nie mogę dokładnie określić jakie komunikaty wyrzucał OpenOCD. Zrobię to wieczorem i najpewniej...

Mikrokontrolery AVR

27 Lis 2017 17:10

Odpowiedzi: 20 Wyświetleń: 1515

-

Mam problem z zestawem Eclipse Kepler + GDB + CS + openOCD 0.8.0 + STM32F072BDISCOVERY z procesorem STM32F072RB (Cortex-M0) i programatorem Stlink. Środowisko jest poprawnie skonfigurowane i działa poprawnie na procesorze STM32F103, tyle że z openOCD 0.7.0. Jako że nowy model procka, musiałem użyć openOCD 0.8.0. Jednak po skompilowaniu programu (poprawne)...

Mikrokontrolery ARM

02 Lis 2014 15:25

Odpowiedzi: 17 Wyświetleń: 2847

-

No jakoś nie ściągałem nowego. Ale czym prędzej to zrobię =] To pomoże ? Bo w sumie ten OpenOCD bez problemów działa z ARM7 i Cortexami. EDIT: Odpaliłem nowe OpenOCD (pobrane z Twojej strony) i mam komunikat: E:\Projekty\ARM\Eclipse\STR91x_examp... -f str912.cfg Open On-Chip Debugger 0.4.0 (2010-02-22-19:05) Licensed under...

Mikrokontrolery ARM

11 Mar 2010 21:12

Odpowiedzi: 8 Wyświetleń: 2427

-

Witam! Po latach odkopałem "bohatera wątku" i próbuję go odpalić. Niestety nie chce zbytnio współpracować a openocd wypisuje co następuje: C:\Documents and Settings\dell>openocd -f interface/jtagkey.cfg -f target/stm32f 1x.cfg Open On-Chip Debugger 0.8.0-dev-00277-g871b34c (2013-12-15-11:29) Licensed under GNU GPL v2 For bug reports,...

Mikrokontrolery ARM

17 Gru 2013 23:37

Odpowiedzi: 353 Wyświetleń: 94599

-

Profilaktycznie spróbuj tak: openocd -f ... -f ... -c "reset_config trst_and_srst; adapter_khz 1;" Jeśli oczywiście masz podłączone obydwa resety. Spróbuj też najnowszego OpenOCD. No i pokaż schemat (; 4\/3!!

Mikrokontrolery ARM

10 Paź 2012 17:29

Odpowiedzi: 2 Wyświetleń: 2070

-

Witam! Od kilku dni zacząłem się wgłębiać w ARM-y i pierwsze co to zabrałem się za instalacje środowiska. Wybrałem CodeSource+Eclipse+OpenOCD do debugowania. O ile kompilator jako tako działa(coś się kompiluje i pojawia się hex) to debuger uparcie do końca nie chce się skonfigurować. Oto jedna z ostatnich sesji: Open On-Chip Debugger 0.2.0 (2009-07-18-09:50)...

Mikrokontrolery ARM

21 Lip 2009 03:07

Odpowiedzi: 4 Wyświetleń: 5124

-

próbuję skonfigurować mój interfejs jtag (boff bf30 na ft2232) do mojego urządzenia at91sam9g45 . Musiałem zrobić niestandardowy kabelek, gdyż na urządzeniu 20złącze jest dla rastra 2mm. Poniżej zamieszczam output z openocd oraz mój konfig - widać, że coś jest nie tak. Myślałem, ze to wina kabla, ale przecież jtag wykrywa urządzenia (Info : JTAG tap:...

Mikrokontrolery ARM

21 Lut 2012 08:08

Odpowiedzi: 1 Wyświetleń: 1364

-

No więc po kolei 1. Skopiować jakiś zbliżony plik i zmienić mu nazwę na lpc2378. Niech będzie to plik lpc2148.cfg if { [info exists CHIPNAME] } { set _CHIPNAME $CHIPNAME } else { set _CHIPNAME lpc2148 } if { [info exists ENDIAN] } { set _ENDIAN $ENDIAN } else { set _ENDIAN little...

Mikrokontrolery ARM

25 Maj 2009 20:46

Odpowiedzi: 13 Wyświetleń: 3306

-

1. Upewnij się, że OpenOCD ma skonfigurowane reset_config na "separate". 2. Upewnij się, że w komendach startowych dla GDB jest "monitor halt reset" 3. Poniżej tej komendy dodaj "monitor mww adres wartosc" (adres - adres rejestru MEMMAP, wartosc - wartość która ustawi "normalne" mapowanie pamięci). Zauważ, że po resecie włącza Ci się bootloader (pc...

Mikrokontrolery ARM

20 Lut 2013 16:10

Odpowiedzi: 10 Wyświetleń: 3011

-

Mam prośbę - sprawdź u siebie czy plik konfiguracyjny o takiej zawartości działa prawidłowo i daj mi znać. Warto się upewnić zanim wyślę go na listę dyskusyjną OpenOCD. Z racji tego, że używasz Wiggler'a to wywal tą ostatnią linijkę ("jtag_rclk..."). # NXP LPC2478 ARM7TDMI-S with 512kB Flash and 64kB Local On-Chip SRAM (98kB total), clocked...

Mikrokontrolery ARM

27 Paź 2011 07:11

Odpowiedzi: 103 Wyświetleń: 17389

-

Mój config: # NXP LPC1768 Cortex-M3 with 512kB Flash and 32kB+32kB Local On-Chip SRAM, clocked with 4MHz internal RC oscillator if { Wgrywam aplikację ze strony: http://tenuki.fr/nio101/?page_id=117 Komenda do OpenOCD: openocd -f LPC1756.cfg -c "init" -c "reset halt" -c "flash write_image erase lpc1756.elf" -c "reset run" -c "shutdown" I otrzymuję komunikat:...

Mikrokontrolery ARM

20 Kwi 2011 18:50

Odpowiedzi: 22 Wyświetleń: 4872

-

Witam, Korzystajac z .text .global _start _start: (at) Label, not really required mov r0, #5 (at) Load register r0 with the value 5 mov r1, #4 (at) Load register r1 with the value 4 add r2, r1, r0 (at) Add r0 and r1 and store in r2 stop: b stop (at) Infinite loop to stop execution 2. Kompilacja: $ arm-none-eabi-gcc -o program pierwszy.S $ file...

Mikrokontrolery ARM

11 Sty 2011 16:49

Odpowiedzi: 8 Wyświetleń: 4864

-

Mam takiego samego oocdlinka, początkowo tez miałem problemy z odpaleniem debuggowania. W moim przypadku (używam ARM mod II, mam dwie linie resetu) pomogła, zmiana ustawień z liniami resetu na następującą (w pliku stm32.cfg): #use combined on interfaces or targets that can't set TRST/SRST separately reset_config trst_only trst_push_pull Jeśli u Ciebie...

Mikrokontrolery ARM

17 Gru 2009 09:02

Odpowiedzi: 4 Wyświetleń: 3046

-

Witam Nie potrafię tego procka zaprogramować. Miałem go na układzie z wyprowadzeniami UART1 + BOOT1 i 0 Próbowałem programować lock pickiem od freddiego (wyjście UART, bootloader) ale nic z tego (a wcześniej programowałem bliźniaczy układ STM32F103R4T6A taką samą metodą i poszło bezproblemowo). Następnie wyprowadziłem pełnego JTAGA z pinów procesora,...

Mikrokontrolery ARM

31 Sie 2013 16:24

Odpowiedzi: 8 Wyświetleń: 2397

-

mam taki plik konfiguracyjny: # target: lm3s8962 if { [info exists CHIPNAME] } { set _CHIPNAME $CHIPNAME } else { set _CHIPNAME lm3s8962 } if { [info exists CPUTAPID ] } { set _CPUTAPID $CPUTAPID } else { set _CPUTAPID 0x3ba00477 } jtag_khz 500 jtag_nsrst_delay 100 jtag_ntrst_delay...

Mikrokontrolery ARM

28 Lut 2011 18:05

Odpowiedzi: 6 Wyświetleń: 1753

-

Może w programie wyłączyłeś interfejs JTAG lub coś w ten deseń? Jeśli po przełączeniu w tryb bootloadera (piny BOOT0 i BOOT1) wciąż nic się nie da zrobić to chyba "po sprawie". Możesz też spróbować łaczyć się trzymając przycisk reset na płytce (jest też do tego specjalna opcja w OpenOCD jako dodatkowy parametr dla reset_config - sprawdź w manualu)....

Mikrokontrolery ARM

03 Lut 2014 18:12

Odpowiedzi: 7 Wyświetleń: 2637

-

Witam, Zacząłem pisać pod ARMy i na samym początku napotkałem dziwny problem. Program pisany w WinARM, programuje klonem wigglera ze środowiska WinARM. Pierwszy programem miał być bootloader. Ściągnąłem bootloader ze strony ST połączyłem z przykładami ze strony ST. Kompiluje wrzucam do procesora i program startuje po... 4 minutach. To że program startuje...

Mikrokontrolery ARM

03 Wrz 2009 17:37

Odpowiedzi: 3 Wyświetleń: 1548

-

W STM32 rezystory pull-up / -down są w ogóle nie potrzebne, za to brak jakiegokolwiek rezystora na linii resetu raczej nie jest normalny... Czy jesteś pewny, że JTAG i / lub płytka są sprawne? Możesz spróbować do wywołania OpenOCD dodać: -c "reset_config trst_and_srst srst_push_pull" Jaka to wersja OpenOCD? 4\/3!!

Mikrokontrolery ARM

17 Lut 2012 14:59

Odpowiedzi: 20 Wyświetleń: 4073

-

Skompilowałem openocd wydając polecenia: ./configure --enable-parport --enable-parport_ppdev make Przełączyłem się nawet na konto root'a ale dalej to samo. EDIT: Spróbowałem skompilować z opcją: ./configure --enable-parport --disable-parport_ppdev Jednak teraz wywala: Open On-Chip Debugger 0.5.0 (2012-01-31-14:10) Licensed under GNU GPL v2 For bug reports,...

Mikrokontrolery ARM

31 Sty 2012 22:52

Odpowiedzi: 8 Wyświetleń: 2244

-

Piszę w zastępstwie kolegi który gdzieś zdobył STM32F0DISCOVERY (nie potrafi załozyć konta na elektrodzie gdyż nie dochodzi do niego mail potwierdzeniem) Instalacja Sourcery G++ Lite przebiegła prawidłowo, ścieżki dodane itp. Instalacja OpenOCD 0.6.1 przebiegła trochę na około (instalacja wersji 0.4.0 a później podmiana plików) Stlink v2 zainstalował...

Mikrokontrolery ARM

05 Lip 2014 16:55

Odpowiedzi: 298 Wyświetleń: 64856

-

Odswiezam temat, bo napotkałem kolejny problem: mianowicie nie mogę ani zaprogramować ani wyczyścić flasha. Probowałem to zrobić tak:[syntax=bash]flash write_image erase RTOSDemo.elf auto erase enabled Padding image section 0 with 2 bytes error erasing flash bank, status: 0xa2 failed erasing sectors 0 to 0 in procedure 'flash' [/syntax] lub po prostu...

Mikrokontrolery ARM

19 Paź 2012 12:54

Odpowiedzi: 35 Wyświetleń: 3423

-

Ciekawa sprawa. Miałem błędy w konfiguracji eclipse i pewnie nadal mam. Nadal próbuje przekompilować pliki z demo dla mojego discovery. Okazało się że zapomniałem pokazać linkerowi gdzie jest skrypt ld. Jak to zrobiłem to wszystko poszło dobrze... Prawie. Załadował się program i widziałem nawet w okienku disassemberta jego dok, można było robić pracę...

Mikrokontrolery ARM

25 Lip 2013 01:00

Odpowiedzi: 5 Wyświetleń: 1806

-

Ok Sorry, poniżej znajduje się plik usbscarab2.cfg... wywołuję go taką składnią kodu "-f usbscarab2.cfg" Plik cfg znajduje się katalogu D:\Yagarto\openOCD\bin\ W External Tools Configuration: podaje ścieżkę location : D:\Yagarto\OpenOCD\bin\openocd.exe oraz Working Directory D:\Yagarto\openOCD\bin Przy uruchamianiu OpenOCD wyskakuje taki komunikat:...

Mikrokontrolery ARM

18 Paź 2010 12:52

Odpowiedzi: 37 Wyświetleń: 7591

-

Tak, to DIY. Ustawianie czegokolwiek w debuggerze nic nie da skoro openocd nie łączy się i kończy działanie. W plikach nic nie zmieniałem, oto one: stlink-v2.cfg stm32f4.cfg Only debugging on evaluation boards is allowed. Debugging on custom hardware is not supported and not allowed

Mikrokontrolery ARM

03 Wrz 2019 14:58

Odpowiedzi: 17 Wyświetleń: 825

-

raczej z roota: usermod -aG plugdev user Ale tym się nie przejmuje, z tym sobie jakoś tam poradze. Na problem z ID też wpadłem i stosownie zmieniłem w configu. Problem jest po połączeniu się z gdb przez [syntax=bash]target remote :3333[/syntax] Wyrzuca to: [syntax=bash] Info : accepting 'gdb' connection on tcp/3333 Error: avr32_ap7k_get_gdb_reg_list:...

Mikrokontrolery AVR

23 Lis 2017 18:51

Odpowiedzi: 16 Wyświetleń: 1368

-

Zignoruj ten error, a komendę zmień na trochę inną: reset_config trst_and_srst trst_pulls_srst jak zadziała to poexperymentuj z reset_config trst_and_srst separate 4\/3!!

Mikrokontrolery ARM

12 Maj 2012 15:59

Odpowiedzi: 27 Wyświetleń: 3400

-

Witam, Uzywam ARMa firmy ST str711. Mam napisany bootloader pochodzacy z pewnego zrodla i dzialajacy na 100%, ktory po zaladowaniu przez JTAGa (Open OCD), umozliwia programowanie uC przez UART0 do 5 sekund po resecie. Bootloader laduje pliki bin bez zadnych problemow, tyle ze uC nie wykonuje zawartego w nich programu. W celu weryfikacji zainstalowalem...

Mikrokontrolery

31 Gru 2009 06:52

Odpowiedzi: 1 Wyświetleń: 1286

-

Niewiem czy to będzie przyczyna ale jeżeli projekt jest dobrze skompilowany to być może coś ważnego nie dodałem lub wpisałem za dużo w pliku *.cfg gdyż oryginalny był pod OpenOCD 0.1.0 a jak mam OpenOCD 0.2.0. Oto mój: #daemon configuration telnet_port 4444 gdb_port 3333 #interface interface parport parport_port 0x378 parport_cable wiggler jtag_speed...

Mikrokontrolery ARM

26 Lis 2009 11:44

Odpowiedzi: 16 Wyświetleń: 3265

-

Witam. Próbuję nieudolnie połączyć się z mikrokontrolerem. Przy próbie programowania otrzymuję następujące komunikaty i błąd: Licensed under GNU GPL v2 For bug reports, read http://openocd.sourceforge.net/doc/d... Info : This adapter doesn't support configurable speed Info : STLINK v2 JTAG v20 API v2 SWIM v0 VID 0x0483 PID 0x3748...

Mikrokontrolery ARM

19 Paź 2014 17:35

Odpowiedzi: 4 Wyświetleń: 1860

-

Używam KT-LINK, OpenOCD 0.7.0, libusb. Środowisko działa prawidłowo, kilka identycznych płyt z STM32F4xx działa prawidłowo, debug, flash itp. Jedna idzie opornie. Po podłączeniu się OpenOCD: Open On-Chip Debugger 0.7.0 (2013-05-05-10:41) Licensed under GNU GPL v2 For bug reports, read http://openocd.sourceforge.net/doc/d...

Mikrokontrolery ARM

13 Gru 2013 21:16

Odpowiedzi: 8 Wyświetleń: 1890

-

Wczoraj wróciłem do tego i cały dzień działało bez problemów programowanie wszystko było ok. Dziś postanowiłem znów zaprogramować, oczywiście w połączeniach nic nie zmieniałem wszystko jest ok i mam taki błąd: [syntax=c]C:\Users\michal\Desktop\openoc... -f interface /zl24prg.cfg -f target/lpc2148.cfg -c targets -c "init"...

Mikrokontrolery ARM

09 Lis 2013 09:26

Odpowiedzi: 57 Wyświetleń: 5868

-

Nie nie nie nie nie... Ludzie - skąd wy bierzecie ciągle tą komendę "soft_reset_halt"? Czemu nie można po prostu zrobić "reset halt" tylko ciągle soft_...? Jak Ci nie działa normalne reset halt, to dodaj może do wywołania OpenOCD coś takiego: -c "reset_config trst_and_srst" 4\/3!!

Mikrokontrolery ARM

14 Lip 2012 14:57

Odpowiedzi: 38 Wyświetleń: 7957

-

Mam pewien problem. OpenOCD wywołuję tak: -f interface/ftdi/jtag-lock-pick_tiny_2.cfg -c "transport select swd;" -f ${workspace_loc}\Termometr\deb... Zawartość pliku dbg.cfg: set CHIPNAME f1 source [find target/stm32f1x.cfg] configure -work-area-size 2048 Po połączeniu dostaję: Open On-Chip Debugger 0.9.0-dev-00067-g2502d8a...

Mikrokontrolery ARM

12 Wrz 2015 23:03

Odpowiedzi: 43 Wyświetleń: 8238

-

A ponieważ wygląda na to, że w mikrokontrolerze już znajduje się program który uniemożliwia połączenie z debuggerem do skasowania go konieczne będzie połączenie w trakcie resetu. Dodaj do wywołania OpenOCD -c "reset_config srst_only srst_nogate connect_assert_srst"

Mikrokontrolery

21 Gru 2015 22:16

Odpowiedzi: 12 Wyświetleń: 1581

-

Witam. Od kilku dni próbuje uruchomić układ z LPC2214. Środowisko skonfigurowałem (Eclipse, OOCD, Yagarto), komunikacja z procesorem jest, program do pamięci jest wysyłany ale jego odzwierciadlania w układzie rzeczywistym nie ma. Jeśli ktoś pracował na takim układzie proszę o kontakt. Poniżej zamieszczam skrypty OOCD: JTAG: interface ft2232 ft2232_device_desc...

Mikrokontrolery ARM

10 Maj 2010 22:26

Odpowiedzi: 14 Wyświetleń: 1892

-

Więc tak, projekt udało mi się dobrze skompilować tylko teraz nie mogę wgrać ani zdebuggować. Gdy włączam OpenOCD to daj mi taki komunikat: Open On-Chip Debugger 0.5.0-dev (2011-06-07-18:11) Licensed under GNU GPL v2 For bug reports, read http://openocd.berlios.de/doc/doxyge... Info : only one transport option; autoselect...

Mikrokontrolery ARM

09 Wrz 2011 18:28

Odpowiedzi: 10 Wyświetleń: 1927

-

Witam, próbuję już drugi dzień zmusić OpenOCD do debugowania programu dla LPC1114 po SWD. Znalazłem w internecie skryp do OpenOCD Open On-Chip Debugger 0.6.0-dev (2012-12-13-17:20) Licensed under GNU GPL v2 For bug reports, read http://openocd.sourceforge.net/doc/d... Info : OpenOCD runs in SWD mode 1 kHz adapter_nsrst_delay:...

Mikrokontrolery ARM

15 Gru 2012 09:49

Odpowiedzi: 3 Wyświetleń: 2958

-

Witam Mam problem z wgraniem programu do sam7s256 za pomocą JTAG i programu Openocd dostaje taki błąd: http://obrazki.elektroda.net/36_12724050... moje pliki konfiguracyjne: ft.cfg #interface interface ft2232 ft2232_layout oocdlink ft2232_vid_pid 0x0403 0x6010 ft2232_device_desc "OOCDLink A" sam7s256.cfg ########################################...

Mikrokontrolery ARM

03 Maj 2010 19:11

Odpowiedzi: 9 Wyświetleń: 2238

-

Jako, że kiedyś szukałem i nie znalazłem odpowiedzi na forum chciałem się podzielić informacją jak wykonać taką zmianę. Podejrzewam, że w drugą stronę (czyli z Annex-A na B) też nie będzie problemu. Co potrzebujemy: Hardware: - JTAG - Modem Software: - OpenOCD (poniższy opis odnosi się do wersji pod Windows) - pliki firmware (x-boot.img, x.img oraz...

Sieci LAN

24 Paź 2013 12:02

Odpowiedzi: 1 Wyświetleń: 2106

-

czesc, Nie moge zmusic JTAGa do pracy. Uzywam a) Yagarto Toolchain do kompilacji b) OpenOCD do programowanie Probuje zaprogramowac AT91SAM7S256 (text on chip AU without number). Uzywam plyty ewaluacyjnej ZL11ARM modulu ZL12ARM. Posiadam KrisTech USB JTAG (UsbScarab2). Moge zaprogramowac flash programem SAM-BA v1.1 (ale juz nie wersja pozniejsza) po...

Mikrokontrolery

08 Lip 2009 07:30

Odpowiedzi: 8 Wyświetleń: 4277

-

Witam Mam problem z flashowaniem procka lpc2917. Nabyłem takowy ponieważ doczytałem, że od wersji 0.3.1 openocd jest wsparcie dla tych scalaków. Niestety OpenOCD nie chce 'rozmawiać' z moim scalakiem. Poniżej zamieszczam mój skrypt, z którym wywołuję openocd jtag_khz100 set FLASH_CLOCK 1024 source [find C:\\Program\ Files\\OpenOCD\\0.4.0\\interface\\turtel...

Mikrokontrolery ARM

25 Lis 2010 09:33

Odpowiedzi: 9 Wyświetleń: 1779

-

Witam! Ja jeszcze chciałbym wrócić do kwestii konfiguracji OpenOCD. Posiadam programator Wiggler i moduł z lpc2368 oraz OpenOCD 0.2.0+Eclipse+CodeSourcery. Przerobiłem plik parport.cfg na #Daemon telnet_port 4444 gdb_port 2001 #JTAG interface parport jtag_speed 4 jtag_device 4 0x01 0x0f 0x0e parport_port 0x378 parport_cable wiggler oraz plik lpc2368.cfg...

Mikrokontrolery ARM

22 Wrz 2017 13:17

Odpowiedzi: 374 Wyświetleń: 133913

-

Koledzy, mam ostatnio taki problem dziwny, bo jak długo programuję STMy takiego nie miałem. Wcześniej używałem cały czas CodeSourcery lub Linaro. Teraz zmieniłem komputer i się zdziwiłem. Dorwałem tylko jakąś ostatnią wersję toolchaina CodeSourcery. Mam jednak taki problem: Łącze się z procesorem (STM32f103C8t6) przez openocd. Open On-Chip Debugger...

Mikrokontrolery ARM

05 Gru 2016 13:27

Odpowiedzi: 27 Wyświetleń: 1743

-

zapewne wgrywasz program do RAMu, skad ginie on po zaniku zasilania. kod znajduje się we flashu. Po włączeniu zasilania i "reset & debug" procek nie jest ponownie programowany, tylko rusza natychmiast debug. W build Config. THUMB Flash Relase jest zaznaczone: Flash, Relase, THUMB. Plik hex z kodem weryfikowany z zawartoscia flasha procka jest ok (h-jtag)....

Mikrokontrolery ARM

06 Lip 2011 16:49

Odpowiedzi: 11 Wyświetleń: 4166

-

Witam, męczę się już drugi dzień z płytką STM32VLDiscovery za pomocą OpenOCD, dodam że F4Discovery śmiga bezbłędnie. Utworzyłem prosty programik standardowo migający diodą w celu przetestowania. Programik kompiluje się bezbłędnie, OpenOCD łączy się z procesorem tez bez żadnych problemów. Problem pojawia się przy próbie debugowania przy starcie program...

Mikrokontrolery ARM

29 Wrz 2014 19:06

Odpowiedzi: 34 Wyświetleń: 2826

-

Witam, Mam nadzieję, że ktoś tu jeszcze zagląda. Mam generalnie problem ze stabilnym działaniem debugowania pod eclipsem. Ale może po kolei. Na razie odstawiłem eclipse'a i programuję procka z linii poleceń komendą: openocd-0.5.0 -f interface/olimex-arm-usb-ocd.cfg -f target/lpc2368.cfg -c"init; reset halt; flash write_image erase d:/Projekty/MIK/Oprogramowanie/lpc-2...

Mikrokontrolery ARM

11 Gru 2012 11:43

Odpowiedzi: 45 Wyświetleń: 7696

-

Witam! Postanowiłem skorzystać z otwartych narzędzi do debogowania. Niestety nie za bardzo funkcjonuje... Open On-Chip Debugger 0.5.0 (2011-08-26-10:27) Licensed under GNU GPL v2 For bug reports, read http://openocd.berlios.de/doc/doxyge... Info : only one transport option; autoselect 'jtag' init_targets Warning - assuming...

Mikrokontrolery ARM

17 Paź 2011 22:43

Odpowiedzi: 6 Wyświetleń: 2127

-

plan sytuacji: bawie sie zestawem ZL9ARM + ZL10ARM z BTC - jest to procek LPC2148. do niego podpinam JTAGa na USB, ktorego dzis sam zmontowalem - bazujac na Turtelizerze 2. opis problemu: problem polega na tym, ze czasem JTAG nie potrafi zatrzymac rdzenia procesora. Dzieje sie to tylko przy uruchamianiu serwera openocd - czasem zglasza on blad: Timed...

Mikrokontrolery

17 Kwi 2008 00:14

Odpowiedzi: 2 Wyświetleń: 1600

-

[url=http://openocd.sourceforge.net/doc/... cortex_m reset_config connect_assert_srst ??

Mikrokontrolery ARM

20 Mar 2014 08:54

Odpowiedzi: 4 Wyświetleń: 1140

-

Po podłączeniu dostaję takie błędy od OpenOCD: Open On-Chip Debugger 0.5.0-dev (2011-06-07-18:11) Licensed under GNU GPL v2 For bug reports, read http://openocd.berlios.de/doc/doxyge... Info : only one transport option; autoselect 'jtag' 1000 kHz adapter_nsrst_delay: 100 jtag_ntrst_delay: 100 #0 : stm32.flash...

Mikrokontrolery ARM

27 Lis 2011 11:34

Odpowiedzi: 17 Wyświetleń: 3040

-

poczyniłem jeszcze taką obserwację, że raz na jakiś czas procek się resetuje poprawnie, wtedy mam output taki **** Build of configuration Debug for project leds2 **** cs-make devrst openocd -f ../scripts/stm32.cfg -c init -c reset run -c shutdown Open On-Chip Debugger 0.3.1 (2009-11-20-00:17) $URL$ For bug reports, read http://openocd.berlios.de/doc/doxyge...

Mikrokontrolery ARM

21 Paź 2010 09:59

Odpowiedzi: 8 Wyświetleń: 3109

-

Witam, Mam trochę problemów z konfiguracją openocd i GDB pod linuxem. Na wstępie zaznaczę, że sprzętowo wszystko powinno być ok, bo całość już kiedyś mi działała ale pracuję teraz na innym komputerze i z nowszymi wersjami oprogramowania. Pierwszy problem to prędkość z jaką łączy się JTAG-lock-pick Freddiego z procesorem. Przy wywołaniu openocd używam...

Mikrokontrolery ARM

12 Sty 2013 21:55

Odpowiedzi: 16 Wyświetleń: 4281

-

Witam! Próbuje rozpocząć debugowanie STM32L476-discovery z wykorzystaniem OpenOCD 0.9.0 pod Eclipse Luna, WIN7 x64. Plik konfiguracyjny zapożyczony z pluginu STM32Cube pod Eclipse gdyż nie znalazłem w oficjalnej wersji OpenOCD. [syntax=stm32l4_cfg] # script for stm32l4x family # # stm32l4 devices support both JTAG and SWD transports. # source [find...

Mikrokontrolery ARM

11 Paź 2015 12:59

Odpowiedzi: 3 Wyświetleń: 1467

-

Doszedłem do tego, że odczytuje mi sygnaturę, ale nic poza tym. Wydaje mi się, że może to być problem z resetem. Ale czy wtedy odczytywana byłaby sygnatura? Przy ustawieniu reset_config trst_and_srst na wyjściu jest: Error: JTAG scan chain interrogation failed: all ones Error: Check JTAG interface, timings, target power, etc. Error:...

Mikrokontrolery ARM

31 Maj 2016 18:45

Odpowiedzi: 6 Wyświetleń: 1707

-

Ok, dzięki za odpowiedzi. Przy uruchamianiu openocd, wskazuję interfejs którego zamierzam użyć: -f interface/jlink.cfg, potem wskazuję -f board/osk5912.cfg (który jest najbliżej tego co potrzebuję), jednak zmodyfikowałem go w ten sposób, że wskazałem tylko jeden bank pamięci, oraz wielkość: source [find target/omap5912.cfg] # NOTE: this...

Mikrokontrolery ARM

15 Mar 2020 22:45

Odpowiedzi: 10 Wyświetleń: 591

-

Witam Posiadam oryginalnego JLinka firmy Segger + sterowniki libusb-win32 1.2.2. Mam problem z połączeniem z targetem w OpenOCD. Używam mikrokontrolera STM32. Takie błędy mi wyskakują: C:\>openocd -f interface/jlink.cfg -f target/stm32.cfg Open On-Chip Debugger 0.4.0 (2010-02-22-19:05) Licensed under GNU GPL v2 For bug reports, read...

Mikrokontrolery ARM

09 Cze 2012 14:29

Odpowiedzi: 11 Wyświetleń: 5873

-

Nie sądzę aby JLink wspierał SWD w OpenOCD. z ST-Link akurat działa. Co do przejściówki, to jest do kupienia w farnellu, ja dałem coś koło 20-30zl chyba. A co do samego miniaturowego złącza - generalnie w JTAGu można się obyć teoretycznie z 5 pinami + masa i napięcie referencyjne (te dwa ostatnie w niektórych przypadkach można sobie darować). Naprawdę...

Mikrokontrolery

12 Sty 2014 23:05

Odpowiedzi: 11 Wyświetleń: 1623

-

Przypadek pierwszy - proponuję spróbować tak: openocd -f ... -f ... -c "adapter_khz 1; reset_config trst_and_srst; init; reset init;" Przypadek drugi - brakuje komendy "init" przed nie-konfiguracyjną komendą "reset ...". Przypadek trzeci - w ogóle nie wiem co to za kosmosy... 4\/3!!

Mikrokontrolery ARM

16 Paź 2012 17:57

Odpowiedzi: 9 Wyświetleń: 2181

-

Dopisz do konfiguracji coś takiego: -c "reset_config none; ..." I użyj normalnej komendy "reset init". Nie wiem też absolutnie po co Ci to "mww 0xE000ED0C 0x05fa0004" ale obstawiam że powinno być usunięte. Przy okazji - w nowych OpenOCD jest taka nowa "uproszczona" komenda do programowania, nazywa się "program" - info jak używać w manualu. 4\/3!!

Mikrokontrolery ARM

27 Mar 2015 23:01

Odpowiedzi: 5 Wyświetleń: 1758

-

Niestety nie pomogło. Prędkość jest była ustawiona domyślna, właśnie 1000kHz, poniżej wklejam wyjście. Open On-Chip Debugger 0.8.0 (2014-06-07-21:57) Licensed under GNU GPL v2 For bug reports, read http://openocd.sourceforge.net/doc/d... WARNING! This file was not tested with real interface, but is assumed to work as this...

Mikrokontrolery ARM

19 Mar 2015 14:47

Odpowiedzi: 7 Wyświetleń: 1215

-

Jakieś sugestie ? Gdyby ktoś miał program do obsługi USART dla STM32F303RC w postaci pliku hex - nie pogardziłbym. Sprawdziłbym czy to wina kompilatora czy STM Edit Przeszedłem na środowisko Eclipse. Fajnie cacy, "obudowałem" sobie kompilator, wrzuciłem taki oto kod: For bug reports, read http://openocd.sourceforge.net/doc/doxyg... Info : This...

Mikrokontrolery ARM

08 Paź 2014 09:51

Odpowiedzi: 15 Wyświetleń: 1389

-

Nie wrzuciłeś skryptu linkera, tylko jeszcze raz wektory... Anyway - jest tam kilka potencjalnych problemów 1 (mało istotny) W skrypcie linkera dodałeś nową sekcję: .ext_mem (NOLOAD) : { *(.ext_mem .ext_mem.*) } > sdram0 jednak według nowej składni powinno być tak: .ext_mem (NOLOAD) : { *(.ext_mem...

Mikrokontrolery ARM

08 Gru 2011 00:57

Odpowiedzi: 6 Wyświetleń: 2326

-

Witam, Jak w temacie, podczas debugowania przez SWD nie działają przerwania. Wersja Openocd 0.9.0 z obsługą SWD od Freddiego. Po sprzętowym resecie bez debugowania przerwania działają. Przez JTAG debugowanie z przerwaniami działa. Skrypt konfiguracyjny Openocd dla SWD: source [find target/swj-dp.tcl] adapter_khz 500 if { [info exists...

Mikrokontrolery

29 Kwi 2016 06:41

Odpowiedzi: 4 Wyświetleń: 561

-

Mam teraz tak: [syntax=c]{ rom (rx): org = 0x08000000, len = 123k m_data (rx) : org = 0x0801EC00, len = 1k ram (rwx): org = 0x20000000, len = 20k } SECTIONS { /* placing my named section at given address: */ .myBufBlock 0x0801EC00 : { KEEP(*(.myBufSection)) /* keep my variable even if not referenced */ } > m_data . . . } const uint CRC_Programu __attribute__((section...

Mikrokontrolery ARM

27 Lut 2018 19:30

Odpowiedzi: 30 Wyświetleń: 2943

-

Może po prostu układ jest fizycznie uszkodzony? Nie mam doświadczenia z tymi układami, jedyne co możesz spróbować, to uruchomić OpenOCD dodając do wywołania coś takiego (na końcu): -c "jtag_khz 1; reset_config trst_and_srst separate" i spróbować ponownie 4\/3!!

Mikrokontrolery ARM

23 Kwi 2012 15:24

Odpowiedzi: 8 Wyświetleń: 1226

-

Generalnie jest tak, że problem powoduje już alokowanie przez funkcję kiss_fftnd_alloc(). Wywołanie wygląda tak, jak powyżej: [syntax=c]config_norm = kiss_fftnd_alloc (dims_obraz, ndims, 0, 0, 0); // position x,x,_0_,x,x tell, that is FFT froward[/syntax] Jej implementacja wygląda tak: [syntax=c]kiss_fftnd_cfg kiss_fftnd_alloc(const int *dims,int ndims,int...

Mikrokontrolery ARM

01 Mar 2018 20:04

Odpowiedzi: 17 Wyświetleń: 828

-

Witam. Próbuje zwiększyć prędkość programowania z wykorzystaniem OpenOCD 0.8.0, programator Atmel SAM-ICE. Plik konfiguracyjny at91sam7x256.cfg z /OpenOCD/share/openocd/scripts/chip/atme... Układ programuje się poprawnie, ale z bardzo niską prędkością - 5KB/s. Komendy: openocd -c "interface jlink" -c "adapter_khz 12000" -f jlink.cfg...

Mikrokontrolery ARM

10 Kwi 2015 07:22

Odpowiedzi: 7 Wyświetleń: 1275

-

Dorzuć do wywołania OpenOCD coś takiego: openocd -f ... -f ... -c "reset_config trst_and_srst" Może pomoże. Jak nie, to może jakimś sposobem zablokował Ci się flash - jak masz wyprowadzony UART i piny BOOT to podłącz się przez ST Flash Loader i zobacz. 4\/3!!

Mikrokontrolery ARM

04 Cze 2012 23:00

Odpowiedzi: 10 Wyświetleń: 2882

-

Ta są te pliki o których pisałeś tylko ja je przekopiowałem do folderu L:\arm. str912.cfg: # script for str9 if { [info exists CHIPNAME] } { set _CHIPNAME $CHIPNAME } else { set _CHIPNAME str912 } if { [info exists ENDIAN] } { set _ENDIAN $ENDIAN } else { set _ENDIAN little }...

Mikrokontrolery ARM

11 Lis 2009 21:00

Odpowiedzi: 16 Wyświetleń: 2949

-

witam szanownych forumowiczów, Od jakiegoś czasu próbuje skonfigurować środowisko eclipse aby współpracował z JTAG lock pick według poradnika znajdującego się na stronie Freddie Chopin. zestaw ewaluacyjny z procesorem STM32103vct6 zakupiłem wszystko w komplecie link http://www.elektroda.pl/rtvforum/topic21... Próbowałem już chyba wszystkich kombinacji...

Mikrokontrolery ARM

29 Mar 2014 21:56

Odpowiedzi: 10 Wyświetleń: 2499

-

Witam W końcu dotarła do mnie płytka C:\Users\tomek>openocd -f interface/jlink.cfg -f target/lpc1768.cfg Open On-Chip Debugger 0.5.0 (2011-08-09-23:21) Licensed under GNU GPL v2 For bug reports, read http://openocd.berlios.de/doc/doxyge... Warn : Adapter driver 'jlink' did not declare which transports it allows; assumi...

Mikrokontrolery ARM

05 Sty 2012 19:12

Odpowiedzi: 8 Wyświetleń: 3024

-

Juz przegladałem i dalej nic. Teraz sprawdzam wszystko od początku: 1. Łącze się z openocd 0.1.0 wpisując openocd.exe -f interface/armjtagusb.cfg -f target/at91sam9260.cfg http://obrazki.elektroda.net/15_12430208... 2. Łącze sie za pomocą telnetu wpisując c:/windows/system32/telnet localhost 4444 3.Wpisuje reset run - chyba działa 4.Wpisuje...

Mikrokontrolery ARM

05 Sie 2009 18:15

Odpowiedzi: 10 Wyświetleń: 4079

-

Witam, Od 2 dni walczę z tym błędem: Invalid ACK 0x4 in JTAG-DP transaction Problem powstaje w chwili gdy jest wysyłana CTRL_STAT, który zwraca ACK = 4, taki błąd niestety nie jest nigdzie opisany jedyne wartości jakie może przyjąć ACK to ACK_OK_FAULT, JTAG_ACK_WAIT. Dlatego kieruję do Was pytanie czy ktoś, kto bardziej się orientuje w protokole JTAG-DP,...

Mikrokontrolery ARM

24 Paź 2011 20:55

Odpowiedzi: 2 Wyświetleń: 1520

-

Dziękuję, zmienię składniki oprogramowania zgodnie z sugestią. Dodano po 2 Po wielu "kombinacjach" m.in. ze sterownikami udało mi się uruchomić debugowanie projektu. Problemu jednak jeszcze nie rozwiązałem, bo wszystko działa niestabilnie. Sesję udaje się uruchomić nie za każdym razem. Muszę odłączać i podłączać płytkę Discovery, resetować lub nie itd....

Mikrokontrolery ARM

18 Gru 2013 23:23

Odpowiedzi: 36 Wyświetleń: 6462

-

Udało mi się zapalić diodę tylko wgrywając program za pomocą debuggera zawartego w Crossworksie. Co ciekawe, gdy próbowałem programować flash dostawałem komunikat: Flash Checksum error. Kolejny test jaki wykonałem to zaprogramowanie flasha za pomocą H-Jtaga używając pliku hex wygenerowanego przez Crossworks'a. Procek się programuje, weryfikacja ok,...

Mikrokontrolery ARM

10 Wrz 2009 22:38

Odpowiedzi: 17 Wyświetleń: 2610

-

Witam jak w temacie, po uruchomieniu debug w Eclipse, w consoli odpowiadającej z OpenOCD mam: Open On-Chip Debugger 0.2.0 (2009-07-18-09:50) Release $URL: http://svn.berlios.de/svnroot/repos/... $ For bug reports, read http://svn.berlios.de/svnroot/repos/... parport port = 888...

Mikrokontrolery ARM

28 Gru 2009 20:43

Odpowiedzi: 2 Wyświetleń: 3130

-

Witam Posiadam płytę EVBlpc213/4x firmy Propox + JTAG . Mam problem z debugowaniem. Wszystko działa na komercyjnych narzędziach np Rowley Crossworks i wszystko jest ok. Mam problem z openocd - nie mogę zainicjować urządzenia. Może ktoś ma doświadczenie z tą płytką oraz openocd. Jak Crossworks działa to musi być to jakiś problem konfiguracyjny. Moj skrypt...

Mikrokontrolery

23 Lut 2008 13:05

Odpowiedzi: 2 Wyświetleń: 1392

-

Witam, Jestem dość początkujący jeśli chodzi o STMy dlatego proszę o wyrozumiałość. Do pamięci flash procesora wrzuciłem kod, który prawdopodobnie zawiesza procesor. Od tego momentu nie mogę się połączyć z uC używając OpenOCD. Komunikat j/n: D:\ARM\openocd-0.5.0\bin>openocd-... -f interface/olimex-arm-usb-ocd.cfg - f target/stm32f1x.cfg...

Mikrokontrolery ARM

13 Lip 2012 08:20

Odpowiedzi: 3 Wyświetleń: 1939

-

Gdzieś była konfiguracja JTAG autorstwa (at)xabean. Sprawiłem, że JTAG działa, to te same piny, które są używane do programowania SPI, więc nie musiałem niczego zmieniać. Wrzuć poniższą konfigurację do pliku bk7321t.cfg i uruchom openocd -f bk7321t.cfg, aby go uruchomić. source [find interface/raspberrypi2-native.cfg] ## https://docs.microsoft.com/en-us/win...

Smart Home Poradniki

21 Wrz 2023 17:19

Odpowiedzi: 8 Wyświetleń: 3084

-

Pierwsze pytanie - czy masz 100% pewności, że wgrany firmware jest dobry? Porada nr 1 - zamiast "reset halt" używaj "reset init" Porada nr 2 - są nowsze wersje OpenOCD niż 0.5.0 Porada nr 3 - jeśli Twoja płytka ma połączone sygnały TRST i SRST to uruchom OpenOCD tak: openocd -f interface/jtagkey.cfg -f target/stm32f2x.cfg -c "reset_config trst_and_srst;...

Mikrokontrolery ARM

18 Gru 2012 21:44

Odpowiedzi: 9 Wyświetleń: 2667

-

oto plik konfiguracji 'openocd' który u mnie działał na identycznym sprzęcie: #daemon configuration telnet_port 4444 gdb_port 3333 #interface interface parport parport_port 0x378 parport_cable wiggler jtag_speed 0 #use combined on interfaces or targets that can't set TRST/SRST separately reset_config srst_only srst_pulls_trst # zmiana z srst_only na...

Mikrokontrolery

23 Wrz 2007 14:25

Odpowiedzi: 5 Wyświetleń: 3632

Oliver Heaviside – nie mógł być telegrafistą, więc został pionierem elektrotechniki

Oliver Heaviside – nie mógł być telegrafistą, więc został pionierem elektrotechniki

Prosty przewodnik po konfiguracji Raspberry Pi

Prosty przewodnik po konfiguracji Raspberry Pi

Zakłócenia elektromagnetyczne (EMI): identyfikacja i metody zapobiegania w elektronice

Zakłócenia elektromagnetyczne (EMI): identyfikacja i metody zapobiegania w elektronice

Czym jest indukcyjność i od czego zależy?

Czym jest indukcyjność i od czego zależy?

Śruba, która zakręciła światem: historia wynalazku Henry'ego Phillipsa

Śruba, która zakręciła światem: historia wynalazku Henry'ego Phillipsa

Budowa, zastosowanie i podstawy obsługi oscyloskopu

Budowa, zastosowanie i podstawy obsługi oscyloskopu

Rozpoczynanie pracy z Raspberry Pi AI HAT+

Rozpoczynanie pracy z Raspberry Pi AI HAT+

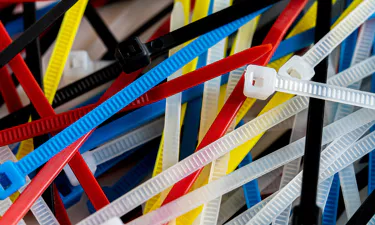

Opaski zaciskowe – podstawy, które powinien znać każdy majsterkowicz

Opaski zaciskowe – podstawy, które powinien znać każdy majsterkowicz

Near Field Communication (NFC): Komunikacja bliskiego zasięgu - zasady działania i zastosowania

Near Field Communication (NFC): Komunikacja bliskiego zasięgu - zasady działania i zastosowania